Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

News

- Home

- News

[News] TSMC to Provide 3DIC Integration for AI Chips in 2027, Featuring 12 HBM4 and Chiplets Manufactured with A16

Jun He, Vice President of Advanced Packaging Technology and Service at TSMC, stated that 3D IC is a crucial method for integrating AI chip memory with logic chips.

According to a report from TechNews, regarding the development of 2.5D CoWoS advanced packaging, which integrates eight chiplets, TSMC will use the A16 advanced process to manufacture the chiplets, and integrated them with 12 HBM4, which is expected to be launched in 2027.

Reportedly, in his speech at the Semicon Taiwan 2024 “3D IC / CoWoS for AI Summit,” He noted that the global semiconductor market is projected to become a trillion-dollar industry by 2030, with HPC and AI being the key drivers, accounting for 40% of the market, which also make AI chips crucial drivers for 3D IC packaging.

The reasons customers choose to manufacture AI chips with 3D IC platform for multi-chiplet design would be related to their lower costs and reduced design transition burdens.

Jun He explained that by converting a traditional SoC+HBM design to a chiplet and HBM architecture, the new logic chip would be the only component that needed to be designed from scratch, while other components such as I/O and SoC can use existing process technologies. This approach reduces mass production costs by up to 76%.

Although the new architecture might increase production costs by 2%, the total cost of ownership (TCO) is improved by 22% due to these efficiencies, He noted.

However, 3D IC still faces challenges, particularly in increasing production capacity. Jun He emphasized that the key to enhancing 3D IC capacity lies in the size of the chips and the complexity of the manufacturing process.

Regarding chip size, larger chips can accommodate more chiplets, improving performance. However, this also increases the complexity of the process, which can be three times more challenging. Additionally, there are risks associated with chip misalignment, breakage, and failure during extraction.

To address these risk challenges, Jun He identified three key factors: tool automation and standardization, process control and quality, and the support of the 3DFabric manufacturing platform.

For tool automation and standardization, TSMC’s differentiated capabilities with its tool suppliers are crucial. With 64 suppliers now involved, TSMC has gained the ability to lead in advanced packaging tools.

In terms of process control and quality, TSMC utilizes high-resolution PnP tools and AI-driven quality control to ensure comprehensive and robust quality management. Finally, the 3DFabric manufacturing platform integrates 1,500 types of materials within the supply chain to achieve optimization.

Read more

- [News] TSMC Plans Rapid CoWoS Expansion Through 2026 in Response to Client Demand

- [News] TSMC Rumored to Build New CoWoS Plant in Southern Taiwan

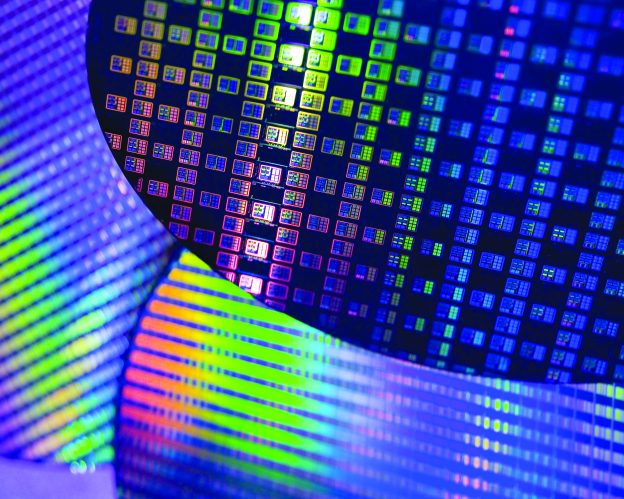

(Photo credit: TSMC)

Please note that this article cites information from TechNews.

Subject

Related Articles

Recent Posts

- [News] Price Hike Impact? PS5 Sales in Japan Plunge Nearly 70%, Hitting a New Low This Year

- [News] More than 30 Projects, Overview of China’s Semiconductor Industry Project Progress in 2024

- [News] China Raises Retirement Age for the First Time in 70 Years

- [News] Samsung Must Boost AI Processor Yields; 3nm Yield Reportedly at 20% in Q2 2024

- [News] AMD Reportedly Accused by Laptop OEMs as It Prioritizes on Enterprise Market

Recent Comments

Archives

- September 2024

- August 2024

- July 2024

- June 2024

- May 2024

- April 2024

- March 2024

- February 2024

- January 2024

- December 2023

- November 2023

- October 2023

- September 2023

- August 2023

- July 2023

- June 2023

- May 2023

- April 2023

- March 2023

- February 2023

- January 2023

- December 2022

- November 2022

- October 2022

- September 2022

- August 2022

- July 2022

- June 2022

- May 2022

- April 2022

- March 2022

- February 2022

- January 2022

- December 2021

- November 2021

- October 2021

- September 2021

- August 2021

- July 2021

- June 2021

- May 2021

- April 2021

- March 2021

- February 2021

- January 2021

Categories

- 5G Technologies

- AR / VR

- Artificial Intelligence

- Automotive Technologies

- Broadband & Home Network

- Cloud / Edge Computing

- Consumer Electronics

- Display

- Display Supply Chain

- Display Technologies

- DRAM

- Emerging Technologies

- Energy

- IC Design

- IC Manufacturing, Package&Test

- Industry 4.0

- IoT

- IR LED / VCSEL / LiDAR Laser

- LCD

- LED

- LED Backlight

- LED Demand / Supply Data Base

- LED Display

- LED Lighting

- Lithium Battery and Energy Storage

- Macroeconomics

- Micro LED / Mini LED

- Monitors / AIO

- NAND Flash

- Notebook Computers

- OLED

- Others

- Panel Industry

- Semiconductors

- server

- Smartphones

- Solar PV

- Tablets

- Telecommunications

- TVs

- Upstream Components

- Wafer Foundries

- Wearable Devices

- 未分類