Popular Keywords

- About Us

-

Research Report

Research Directory

Semiconductors

LED

Consumer Electronics

Emerging Technologies

- Selected Topics

- Membership

- Price Trends

- Press Center

- News

- Events

- Contact Us

News

- Home

- News

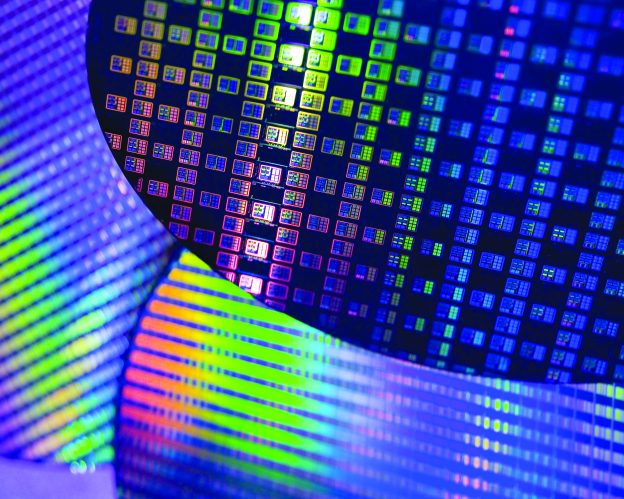

[News] Rumors Suggest TSMC’s 2nm Node First Tool-In with Monthly Production Capacity Unveiled

Despite the uncertainties in the semiconductor market, there is still an intense global competition in the development of advanced semiconductor manufacturing processes. TSMC as one of the key players in the foundry industry is actively advancing its next-generation 2nm process. According to market rumors, the schedule for the first tool-in at Hsinchu Baoshan Fab and Kaohsiung Fab has been established, along with a finalized production capacity plan.

CNA has reported that TSMC’s 2nm process will be deployed in the Phase 2 Expansion Area of the Baoshan Site at the Hsinchu Science Park. The first tool-in is scheduled for April 2024. Industry sources have revealed that the initial production capacity for this process will be around 30,000 wafers per month, with mass production planned for the following year.

In addition, TSMC’s fab in Kaohsiung has notified equipment suppliers that this facility is set to begin in the third quarter of 2025. According to MoneyDJ, the pilot run is planned for the end of the same year, with the aim of achieving mass production in 2026. The Kaohsiung fab will adopt the N2P process, which is an enhanced version of the 2nm process with the backside power rail technology. The initial monthly production capacity is also expected to be around 30,000 wafers.

According to previous disclosures made by TSMC during financial calls, the company has developed a backside power rail solution for the N2 process, which is particularly suitable for high-performance computing (HPC) applications. This innovative technology is expected to boost speed by 10% to 12% and increase logic density by 10% to 15%. TSMC plans to introduce the backside power rail solution to customers in the latter half of 2025, with mass production scheduled for 2026. This timetable aligns with recent rumor circulating in the supply chain.

In addition to the latest progress on the N2P process, TSMC made an official announcement at the IEEE International Electron Devices Meeting (IEDM) on December 12th. Specifically, the company revealed its plans to introduce a 1.4nm process as the successor to the 2nm process. As reported by Tom’s Hardware, this new process, named A14, continues the naming convention from the 2nm process (A20). Production using the A14 process is anticipated to take place between 2027 and 2028.

Please note that this article cites information from CNA, MoneyDJ and Tom’s Hardware

(Image: TSMC)

Explore more

- [News] TSMC Responds to Rumors of New 1.4nm Fab

- [News] TSMC President Highlights 2024 Semiconductor Challenges While Envisioning Abundant AI Opportunities

- [News] TSMC May Reduce Next Year’s Capital Expenditure, Affecting Orders for Equipment & Testing-Related Companies